Bragge Gupt

## JAYPEE UNIVERSITY OF INFORMATION TECHNOLOGY, WAKNAGHAT TEST -2 EXAMINATION- October 2017

B.Tech (ECE) 3rd Semester

COURSE CODE: 10B11EC312

MAX. MARKS: 25

COURSE NAME: Analog Electronics

**COURSE CREDITS: 4**

MAX. TIME: 1.5 Hrs

Note: All questions are compulsory. Carrying of mobile phone during examinations will be treated as case of unfair means.

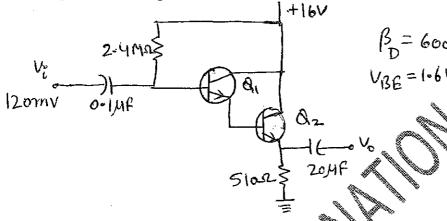

Q1- For the given Darlington transistor draw the ac equivalent circuit,  $r_e$  model and Calculate the voltage gain. Repeat the problem if a resistor  $R_e$ = 200K $\Omega$  is added along with a typess capacitor  $C_E$ . Output is now off the collector of the transistor. In both the cases ignore  $r_o$ . [6]

- Q2- (a) Draw the neat circuit diagram of Emitter follower and show that in emitter follower  $A_{\nu}=1$ . Ignore  $r_0$ .

- (b) Given  $h_{ie} = 2.2 \text{K}\Omega$ ,  $h_{fe} = 100$ ,  $h_{re} = 4 \times 10^{-4}$ , and  $h_{oe} = 25 \mu\text{S}$ , draw the following:

- i. Common Emitter hybrid equivalent model.

- ii. Common Emitter re equivalent model

- iii. Common base hybrid equivalent model

- iv. Common base requivalent model

[2]

[4]

Q3- For voltage divider bias circuit with bypass capacitor  $C_E$ , prove that  $A_{VNL} > A_{VL} > A_{VS}$ . Ignore  $r_0$ .

[6]

[7]

- Q4- For the given eascade system with two identical stages, determine:

- a. The loaded voltage of each stage.

- the total gain of the system (Av5)

- C. The loaded current gain of each stage.

- d. The total current gain of the system

- **e.** How  $Z_i$  is affected by the second stage and  $R_L$ ?

- **f.** How  $Z_o$  is affected by the first stage and  $R_s$

- **g.** The phase relationship between  $V_o$  and  $V_i$ .

RS IMFV CE Amplified CE Amplified  $Z_i = 1 \text{ K}\Omega$   $Z_i = 1 \text{ K}\Omega$   $Z_i = 1 \text{ K}\Omega$   $Z_i = 3.3 \text{ K}\Omega$