# Jaypee University of Information Technology Solan (H.P.) LEARNING RESOURCE CENTER

## Acc. Num. SP07018 Call Num:

### General Guidelines:

- Library books should be used with great care.

- Tearing, folding, cutting of library books or making any marks on them is not permitted and shall lead to disciplinary action.

- Any defect noticed at the time of borrowing books must be brought to the library staff immediately. Otherwise the borrower may be required to replace the book by a new copy.

- ♦ The loss of LRC book(s) must be immediately brought to the notice of the Librarian in writing.

**Learning Resource Centre-JUIT**

SP07018

# SOFTWARE CONTROLLED ROBOTIC ARM MOVEMENT

061463

**ADITYA JAIN**

Dr. RAVI RASTOGI

**MAY 2011**

**A DISSERTATION**

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DGREE OF

BACHELORE OF TECHNOLOGY IN INFORMATION TECHNOLOGY

DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING AND INFORMATION TECHNOLOGY

JAYPEE UNIVERSITY OF INFORMATION TECHNOLOGY WAKNAGHAT, SOLAN, HIMACHAL PRADESH – 173234, INDIA

#### **CERTIFICATE**

This is to certify that the work entitled, "SOFTWARE CONTROLLED ROBOTIC ARM MOVEMENT" submitted by **ADITYA JAIN (061463)** in partial fulfillment for the award of degree of bachelor of technology in INFORMATION TECHNOLOGY of Jaypee University of Information and Technology has been carried out under my supervision. This work has not been submitted partially or wholly to any other University or Institute for the award of this or any other degree or diploma.

Signature of Supervisor:

Name of Supervisor:

Dr. RAVI RASTOGI

Designation:

Lecturer

Date: 23<sup>rd</sup> May 2011

#### **ACKNOWLEDGMENT**

It has been an amazing experience working on the project <u>SOFTWARE</u> <u>CONTROLLED ROBOTIC ARM MOVEMENT</u> Working on a project that involves in depth knowledge of language proves that I as a student have imbibed in us the quality that an Engineer should have.

I thank **Dr. Ravi Rastogi**, our project guide ,who has always encouraged us to put in our best efforts and deliver a quality and professional output .I really thank him for his time and efforts. I am deeply indebted to all those who provided reviews and suggestions for improving the materials and topic covered in our package, and I extend our apologies to anyone we may have failed to mention.

Thank you

Signature:

Name of Student: ADITYA JAIN

Roll Number:

061463

Department of Information Technology Engineering Jaypee University of Information Technology, Solan

Date: 23<sup>rd</sup> May 2011

#### **SUMMARY**

Robots and embedded control systems are traditionally programmed to perform automated tasks, yet accomplishing complicated and dynamically changing tasks will typically require the use of specialized computational resources and software systems. In order to design these sophisticated control systems the use of computational modeling and simulation techniques is necessary to ensure that final implementations of the system perform optimally. Since even the simplest robotic control systems are intrinsically a mixture of heterogeneous sub-systems, each focusing on a particular task, we need a means of modeling the different aspects of the system accurately and intuitively. Using the Ptolemy II software environment, one can visually design and model elaborate control systems by incorporating heterogeneous models of computation that govern the interaction of multiple components within the system. In this paper we design a robot arm controller component for Ptolemy II that enables various other Ptolemy components to interface and control the robot arm in novel ways, hereby expanding the scope of innovative uses and future applications. We then illustrate an implementation of a Ptolemy model that uses an X-10 remote control, communicating via an X-10 network, to control the movements of a Lynx-5 Robot Arm.

Signature of Student Name: Aditya Jain

Date: 23<sup>rd</sup> May 2011

Signature of Supervisor Name: Dr. Ravi Rastogi

Date: 23rd May 2011

### **INDEX**

| <u>CHAPTER</u> <u>Page No.</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.1 CISC (Complex Instruction) 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.2 RISC (Reduced Instruction)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.3 Comparison between CISC and RISC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.4 The Performance Equation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.5 Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.5 Till Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 2: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Chapter 2. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.1 PCB Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

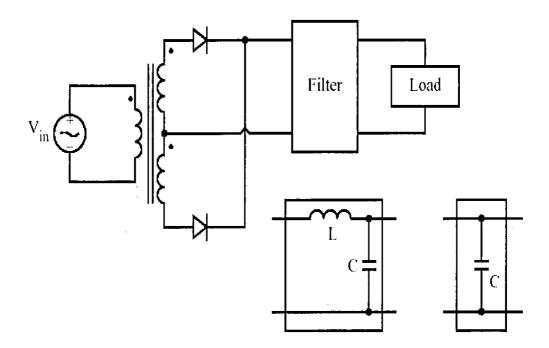

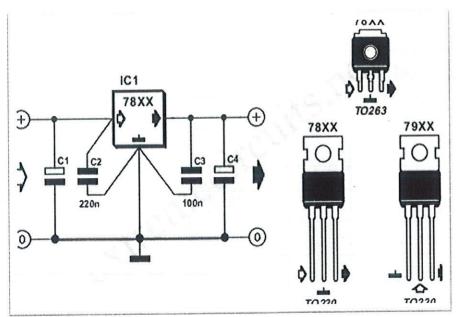

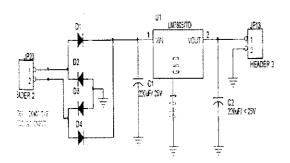

| 2.2 Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.3 Controller Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

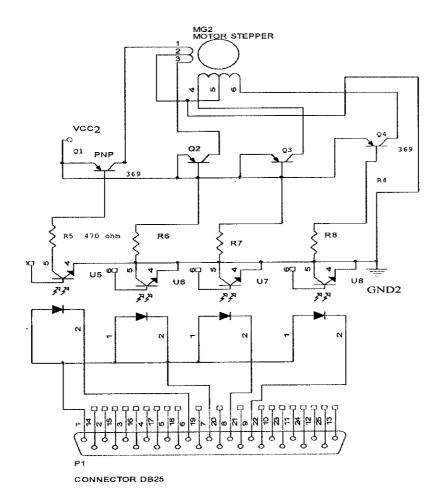

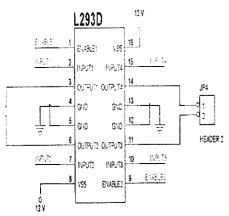

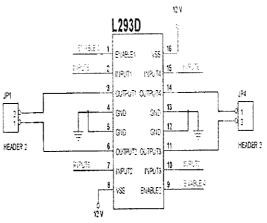

| 2.4 Driver Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| and the second s |

| Chapter 3: System Design And Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1 Semiconductor Diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.2 Rectifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.3 Transformer                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4 Resistor                                                                                                                                                                                                                                    |

| 3.5 Capacitor                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                 |

| Chapter 4 : AVR CPU Core                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                 |

| 4.1 ALU- Arithmetic Logic Unit                                                                                                                                                                                                                  |

| 4.2 Status Register                                                                                                                                                                                                                             |

| 4.3 General Purpose Register File                                                                                                                                                                                                               |

| 4.4 Stack pointer41                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                 |

| hapter 5 : Reset and Interrupt Handling                                                                                                                                                                                                         |

| hapter 5 : Reset and Interrupt Handling                                                                                                                                                                                                         |

| hapter 5 : Reset and Interrupt Handling                                                                                                                                                                                                         |

| Shapter 5 : Reset and Interrupt Handling  5.1 Memories                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                 |

| 5.1 Memories                                                                                                                                                                                                                                    |

| 5.1 Memories       45         5.2 SRAM Data Memory       47                                                                                                                                                                                     |

| 5.1 Memories       45         5.2 SRAM Data Memory       47         5.3 EPROM Data Memory       49                                                                                                                                              |

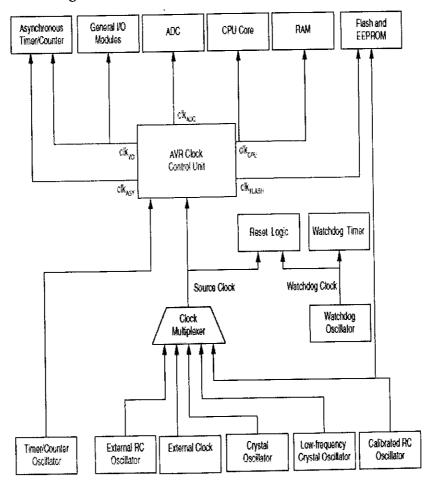

| 5.1 Memories       45         5.2 SRAM Data Memory       47         5.3 EPROM Data Memory       49         5.4 System Clock and Clock Distribution       51                                                                                     |

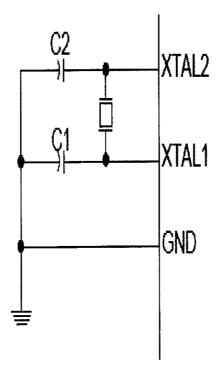

| 5.1 Memories       45         5.2 SRAM Data Memory       47         5.3 EPROM Data Memory       49         5.4 System Clock and Clock Distribution       51         5.5 Crystal Oscillator       53                                             |

| 5.1 Memories       45         5.2 SRAM Data Memory       47         5.3 EPROM Data Memory       49         5.4 System Clock and Clock Distribution       51         5.5 Crystal Oscillator       53                                             |

| 5.1 Memories       45         5.2 SRAM Data Memory       47         5.3 EPROM Data Memory       49         5.4 System Clock and Clock Distribution       51         5.5 Crystal Oscillator       53                                             |

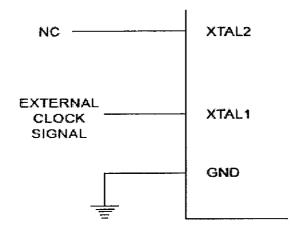

| 5.1 Memories       45         5.2 SRAM Data Memory       47         5.3 EPROM Data Memory       49         5.4 System Clock and Clock Distribution       51         5.5 Crystal Oscillator       53         5.6 External RC Oscillator       54 |

| 5.1 Memories       45         5.2 SRAM Data Memory       47         5.3 EPROM Data Memory       49         5.4 System Clock and Clock Distribution       51         5.5 Crystal Oscillator       53         5.6 External RC Oscillator       54 |

| 5.1 Memories       45         5.2 SRAM Data Memory       47         5.3 EPROM Data Memory       49         5.4 System Clock and Clock Distribution       51         5.5 Crystal Oscillator       53         5.6 External RC Oscillator       54 |

| 6.4 Stepper Motor 68                       |

|--------------------------------------------|

|                                            |

| Chapter 7: Power Management and Sleep mode |

| 7.1 Project Working and Implementation 74  |

| <b>Chapter 8 : CODE</b>                    |

| Chapter 9 : Discussion and Future Scope    |

#### LIST OF FIGURES

| Certificate from the Supervisor<br>Acknowledgement<br>Summary | II<br>III<br>IV |

|---------------------------------------------------------------|-----------------|

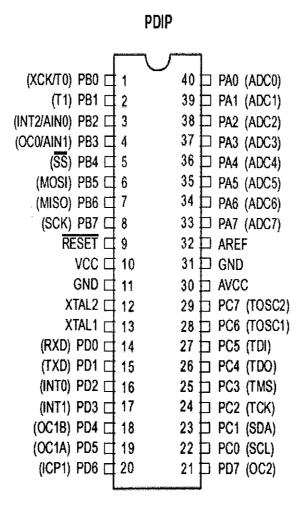

| Fig . 1.1 (Pin diagram)                                       | 13              |

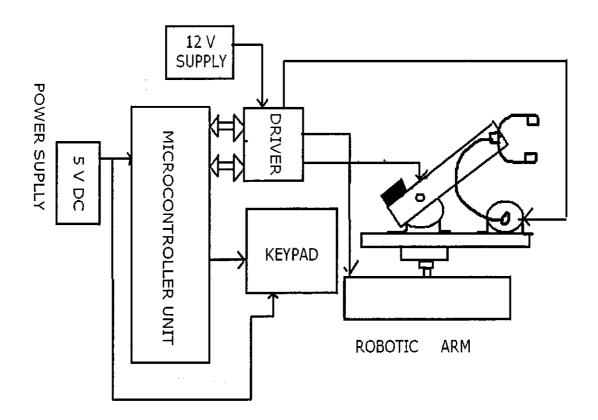

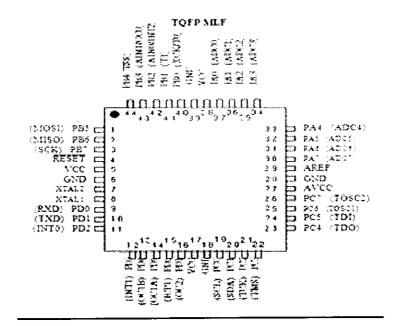

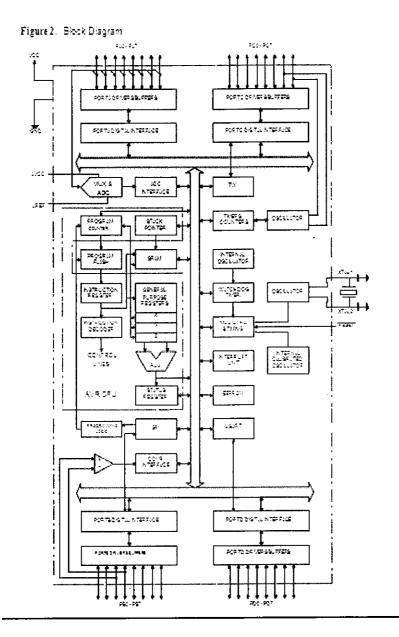

| Fig. 2.1 (Block Diagram)                                      | 20              |

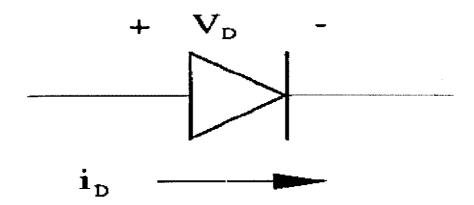

| Fig. 3.1 (Diode)                                              | 23              |

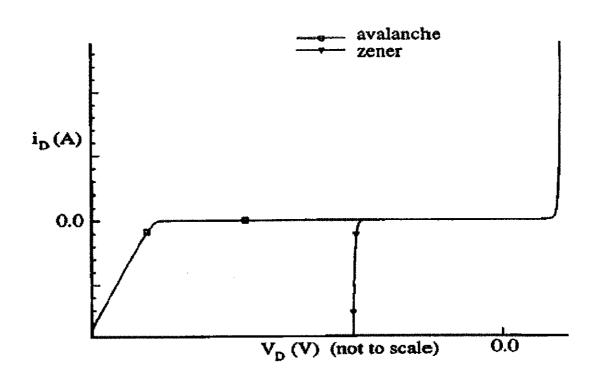

| Fig. 3.2 (Diode DC Characteristics)                           | 24              |

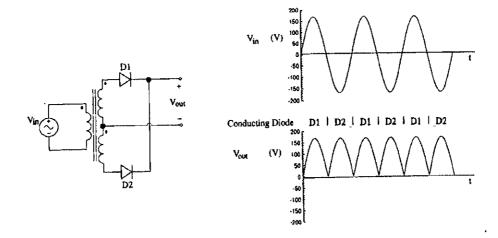

| Fig. 3.3 (Rectifier Characteristics)                          | 25              |

| Fig. 3.4 (Full Wave Rectifier)                                | 26              |

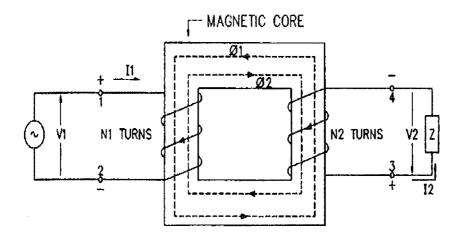

| Fig. 3.5 (Transformer)                                        | 27              |

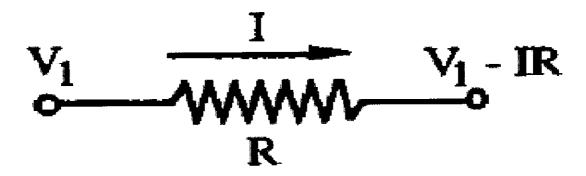

| Fig. 3.6 (Resistor)                                           | 29              |

| Fig. 3.7 (Resistor Working)                                   | 31              |

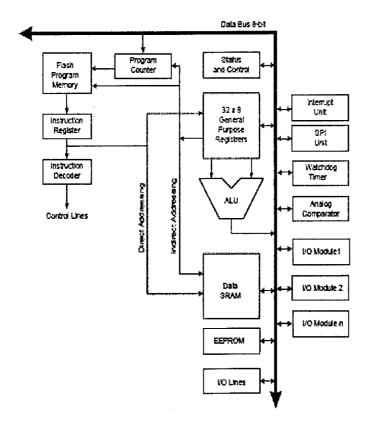

| Fig. 4.1 (AVR MCU Architecture)                               | 33              |

| Fig. 4.2 (AVR Status Register)                                | 36              |

| Fig. 4.3 (AVR CPU General Purpose i                           | register) 38    |

| Fig. 4.4 (Stack Pointer)                                      | 39              |

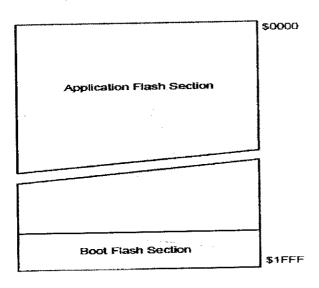

| Fig. 5.1 (Program Memory map)                                 | 43              |

| Fig. 5.2 (Data Memory map)                                    |                 |

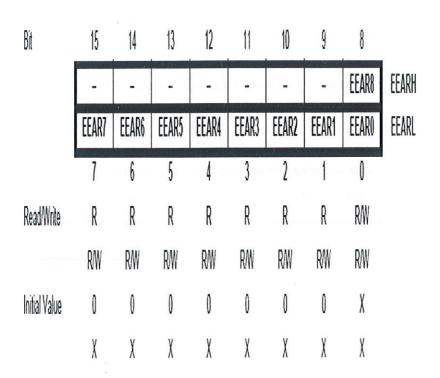

| Fig. 5.3(EPROM Read /Write Access)                            | 47              |

| Fig. 5.4 (System Clock)                                       |                 |

| Fig. 5.5 (Crystal Oscillator)                                 |                 |

| Fig. 5.6 (External Clock)                                     |                 |

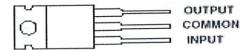

| Fig. 6.1 (78xx)                                               |                 |

| Fig. 6.2                                                      |                 |

| Fig. 6.3 (ATMEGA16)                                           |                 |

| Fig. 6.4 (Block Diagram)        | 59 |

|---------------------------------|----|

| Fig. 6.5 (8086/88 Pin out)      | 61 |

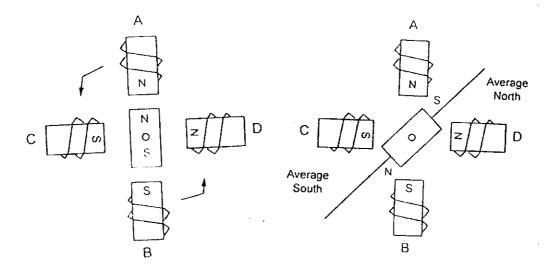

| Fig. 6.6 (Rotor Alignment)      | 67 |

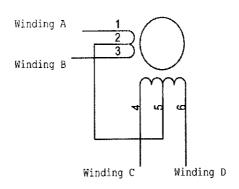

| Fig. 6.7 (Stator Winding)       | 68 |

| Fig. 6.8 (Step Alignment)       | 70 |

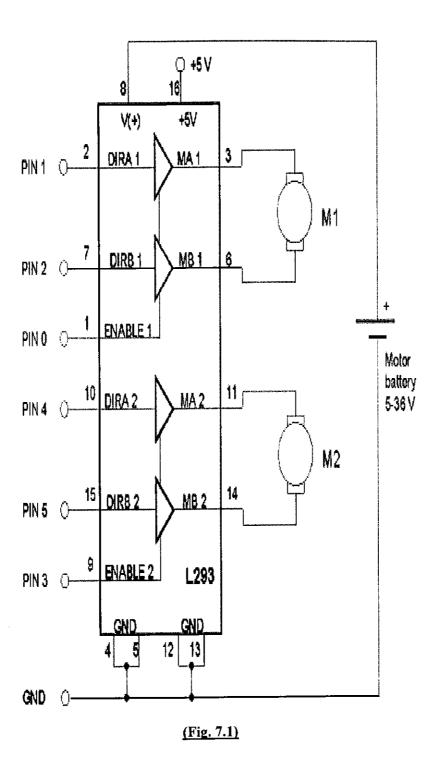

| Fig.7.1                         | 73 |

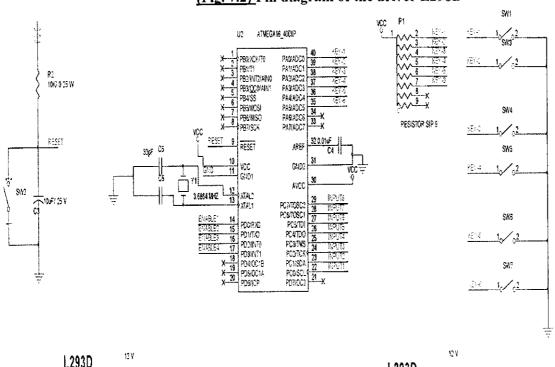

| Fig. 7.2 (Pin Diagram of L298D) | 74 |

.

#### **ABSTRACT**

Robots and embedded control systems are traditionally programmed to perform automated tasks, yet accomplishing complicated and dynamically changing tasks will typically require the use of specialized computational resources and software systems. In order to design these sophisticated control systems the use of computational modeling and simulation techniques is necessary to ensure that final implementations of the system perform optimally. Since even the simplest robotic control systems are intrinsically a mixture of heterogeneous sub-systems, each focusing on a particular task, we need a means of modeling the different aspects of the system accurately and intuitively. Using the Ptolemy II software environment, one can visually design and model elaborate control systems by incorporating heterogeneous models of computation that govern the interaction of multiple components within the system. In this paper we design a robot arm controller component for Ptolemy II that enables various other Ptolemy components to interface and control the robot arm in novel ways, hereby expanding the scope of innovative uses and future applications. We then illustrate an implementation of a Ptolemy model that uses an X-10 remote control, communicating via an X-10 network, to control the movements of a Lynx-5 Robot Arm.

#### **CHAPTER 1: APPRAOCHES**

#### Microcontroller

A microcontroller (sometimes abbreviated  $\mu$ C, uC or (MCU) is a small computer on a single Integrated Circuit containing a processor core, memory and programmable input/output peripherals..Program memory in the form of NOR Flash or OTP ROM is also often included on chip, as well as a typically small amount of RAM. Microcontrollers are designed for embedded applications, in contrast to the microprocessors used in Personal Computers or other general purpose applications.

Microcontrollers are used in automatically controlled products and devices, such as automobile engine control systems, implantable medical devices, remote controls, office machines, appliances, power tools and toys. By reducing the size and cost compared to a design that uses a separate microprocessor, memory and input/output devices, microcontrollers make it economical to digitally control even more devices and processes. Mixed signal microcontrollers are common, integrating analog components needed to control non-digital electronic systems.

#### 1.1: CISC Approach

The primary goal of CISC architecture is to complete a task in as few lines of assembly as possible. This is achieved by building processor hardware that is capable of understanding and executing a series of operations. For this particular task, a CISC processor would come prepared with a specific instruction. When executed, this instruction loads the two values into separate registers, multiplies the operands in the execution unit, and then stores the product in the appropriate register. Thus, the entire

task of multiplying two numbers can be completed with one instruction:

MULT 2:3, 5:2

MULT is what is known as a "complex instruction." It operates directly on the computer's memory banks and does not require the programmer to explicitly call any loading or storing functions. It closely resembles a command in a higher level language. For instance, if we let "a" represent the value of 2:3 and "b" represent the value of 5:2, then this command is identical to the C statement "a = a \* b."

One of the primary advantages of this system is that the compiler has to do very little work to translate a high-level language statement into assembly. Because the length of the code is relatively short, very little RAM is required to store instructions. The emphasis is put on building complex instructions directly into the hardware.

#### 1.2: RISC Approach

RISC processors only use simple instructions that can be executed within one clock cycle. Thus, the "MULT" command described above could be divided into three separate commands: "LOAD," which moves data from the memory bank to a register, "PROD," which finds the product of two operands located within the registers, and "STORE," which moves data from a register to the memory banks. In order to perform the exact series of steps described in the CISC approach, a programmer would need to code four lines of assembly:

| LOAD         | Α, | 2:3 |

|--------------|----|-----|

| LOAD         | В, | 5:2 |

| PROD         | Α, | В   |

| STORE 2:3, A |    |     |

At first, this may seem like a much less efficient way of completing the operation. Because there are more lines of code, more RAM is needed to store the assembly level instructions.

The compiler must also perform more work to convert a high-level language statement into code of this form.

#### 1.3: Comparison

| CISC                                                                  | RISC                                                                       |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------|

| 1) Emphasis on hardware                                               | 1) Emphasis on software                                                    |

| 2) Includes multi-clock complex instructions                          | Single-clock,     reduced instruction only                                 |

| 3) Memory-to-memory:  "LOAD" and "STORE" incorporated in instructions | 3) Register to register:  "LOAD" and "STORE"  are independent instructions |

| 4) Small code sizes, high cycles per second                           | 4) Low cycles per second,<br>large code sizes                              |

| 5) Transistors used for storing complex instructions                  | 5) Spends more transistors on memory registers                             |

However, the RISC strategy also brings some very important advantages. Because each instruction requires only one clock cycle to execute, the entire program will execute in approximately the same amount of time as the multi-cycle "MULT" command. These RISC "reduced instructions" require less transistors of hardware space than the complex instructions, leaving more room for general purpose registers. Because all of the instructions execute in a uniform amount of time (i.e. one clock), pipelining is possible.

Separating the "LOAD" and "STORE" instructions actually reduces the amount of work that the computer must perform. After a CISC-style "MULT" command is executed, the processor automatically erases the registers. If one of the operands needs to be used for another computation, the processor must re-load the data from the memory bank into a register. In RISC, the operand will remain in the register until another value is loaded in its place.

#### 1.4: The Performance Equation

The following equation is commonly used for expressing a computer's performance ability:

$$\frac{\text{time}}{\text{program}} = \frac{\text{time}}{\text{cycle}} \times \frac{\text{cycles}}{\text{instruction}} \times \frac{\text{instructions}}{\text{program}}$$

The CISC approach attempts to minimize the number of instructions per program, sacrificing the number of cycles per instruction. RISC does the opposite, reducing the cycles per instruction at the cost of the number of instructions per program.

The controller which we use in our project is Atmega16 it have following feature

- High-performance, Low-power Atmel® AVR® 8-bit Microcontroller

- Advanced RISC Architecture

- 131 Powerful Instructions Most Single-clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

- High Endurance Non-volatile Memory segments

- 16 Kbytes of In-System Self-programmable Flash program memory

- 512 Bytes EEPROM

- 1 Kbyte Internal SRAM

- Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C(1)

- Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

- Programming Lock for Software Security

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Four PWM Channels

- 8-channel, 10-bit ADC

- 8 Single-ended Channels

- 7 Differential Channels in TQFP Package Only

- 2 Differential Channels with Programmable Gain at 1x, 10x, or 200x

- Byte-oriented Two-wire Serial Interface

- Programmable Serial USART

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby

- I/O and Packages

- 32 Programmable I/O Lines

- 40-pin PDIP, 44-lead TQFP, and 44-pad QFN/MLF

- Operating Voltages

- -2.7V 5.5V for ATmega16L

- -4.5V 5.5V for ATmegal 6

- Speed Grades

- -0-8 MHz for ATmega16L

- -0 16 MHz for ATmegal 6

- Power Consumption @ 1 MHz, 3V, and 25°C for ATmegal6L

- Active: 1.1 mA

- Idle Mode: 0.35 mA

- Power-down Mode: < 1 Ma

Fig. 1.1: PIN DIAGRAM:

#### 1.5: Pin Descriptions

VCC: Digital supply voltage.

even if the clock is not running.

GND: Ground.

**Port A (PA7.....PA0)**: Port A serves as the analog inputs to the A/D Converter. Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active,

**Port B (PB7.....PB0)**: Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active even if the clock is not running.

Port C (PC7....PC0): Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PC5 (TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs. Port C also serves the functions of the JTAG interface and other special features of the ATmega16 as listed.

**Port D (PD7.....PD0)**: Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active even if the clock is not running.

**RESET:** Reset Input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running.

**XTAL1:** Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

XTAL2: Output from the inverting Oscillator amplifier.

**AVCC:** AVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally connected to VCC, even if the ADC is not used. If the ADC is used, it should be connected to VCC through a low-pass filter.

AREF: AREF is the analog reference pin for the A/D Converted

#### **CHAPTER 2: INTRODUCTION**

There are many definitions of robot and no real consensus has been attained so far. We loosely define a robot as follows:

**Robot:** An electromechanical device which is capable of reacting in some way to its environment, and take autonomous decisions or actions in order to achieve a specific task.

These days the industry is depend on the production of the goods at high pace. As we know in Auto industry have so many different task which involve the very hard environment like RIG wielding, spray painting etc. so we try to make our employ safe to work. Even in nuclear plant to deploy nuclear fuel in the reactors, which is one of the dangerous job of the world for men and also we need somebody which not got effected by the radiation emitted by the radioactive material.

Robots used to manipulate objects like bombs or hazardous materials need a robotic arm. Robotic arms usually have several points of articulation or joints. The arm might have the same capabilities of a human arm, with shoulder, elbow and wrist articulation, or it may have many more joints, allowing the operator to reach places he wouldn't be able to get to on his own. On the end of the arm is a manipulator, usually a gripping device in the form of a two-fingered claw.

Because the officer controlling the robot is at least several meters away from the robot, he needs a way to see the robot's environment independent of his own perspective. For this reason, police robots use video cameras to broadcast images back to the operator's laptop or console. Most robots use at least two or three cameras so that the operator can stay aware of the robot's surroundings. Some models have a camera mounted on every

point of articulation, as well as stationary cameras attached to the body of the robot. Video camera systems range from black-and-white to night vision and infrared.

Another feature many police robots have is a two-way audio system. Manufacturers mount microphones and speakers on the robot, allowing police to listen to sounds in the robot's environment or communicate with suspects or hostages in a dangerous situation. The robot can become the eyes and ears of the police force without a single officer being put in harm's way.

Every robot have arm which make him work easily. As every robot arm is free to move in all direction, can hold the object. so it is very important to make robotic arm and make it work manually.

These are the following things which is main part of the any embedded system these are as follows

- 1. PCB design

- 2. Power supply.

- 3. Controller circuit

- 4. Driver circuit

#### 2.1: PCB design

In PCB design we keep in mind that the circuit track should be kept at the mini distance that two track signal should not interfere with the adjusting track. Which result in the induction of the voltage over the other track which ride over the signal. The thickness of the track also decides of the current carrying capacity of the track. So the power track sometime needs to be soldered with extra solder. Printed circuit board (PCB) is a component made of one or more layers of insulating material with electrical conductors. The insulator is typically made on the base of fiber reinforced

resins, ceramics, plastic, or some other dielectric materials. During manufacturing, the portions of conductors that are not needed are etched off, leaving printed circuits that connect electronic components.

Currently the main generic standard for the design of printed circuit boards, regardless of materials, is IPC-2221A. Whether a PCB board is single-sided, double-sided or multilayer, this standard provides rules for manufacturability and quality such as requirements for material properties, criteria for surface plating, conductor thickness, component placement, dimensioning and tolerance rules, and more. For a specific technology, the designer can then choose the appropriate sectional standard from the IPC-2220 series. For power conversion devices, additional parameters are recommended by IPC-9592. The width of the circuit conductors should be chosen based on the maximum temperature rise at the rated current and the acceptable impedance. The spacing between the PC traces is determined by peak working voltage, the coating and the product application. The minimum possible widths of the traces and of the spacing between them are both limited by the manufacturing capabilities of your fabricator and in any case should not be less than 2 mils. Typical minimum values are 6/6 mils. Depending on the application and product end use, other standards may also apply. For example, for mains-powered or battery-powered information technology equipment, the creep age and clearance requirements of IEC/UL 60950-1 shall take precedence over IPC. IPC and other standards do not tell you how to properly route the board. Good PCB layout techniques require an understanding of the effects of non-zero trace impedance and the coupling of signals from one circuit to another through parasitic capacitances and radio transmission, as well as a basic understanding of circuit operation. Auto placement may be done for most parts of control circuits, but power, ground and high di/dt circuits should be routed by hand. Here you will find guidelines for designing PCB, links to software downloads, trace calculators and other info, tools and online resources.

#### 2.2: Power supply

The power supply is the important part of any electronics circuit. if we select under rated power supply (for example if we have circuit which required 12 V, 1 A, if we took 12 V, 750 m A then when it need full current then it result in the dip of voltage supply from 12 to lower voltage and if the circuit is working on the 12 volt and it got low voltage then it effect the working of the electronics chips which are design for particular voltage level. So deign of the power supply according to the circuit is very important.

#### 2.3: Controller selection

Now the selection of the controller depend on the number of input and out to be sense and control. So we must keep in mind that the controls should of pin number according to the it. So if there is only two in and out to be sense and control than we must took low pin controller as if we select controller with more pin it make circuit design then we are going to make bigger circuit which is not the best concept for the embedded.

#### 2.4: Driver circuit

The driver circuit is very important in case of operating the relay a, interface of the two different type of IC with each other as CMOS need less current and other side TTL IC need more current as they are Transistor based IC .also for long distance communication we needed buffer driver circuit in between then we must keep in mind the maxi. Distance that a cable can take signal from one side to other side cable.

#### **Block diagram**

Fig. 2.1

# CHAPTER 3: SYSTEM DESIGNE AND IMPLEMENTATION

#### 3.1: SEMICONDUCTOR DIODE

Generally refers to a two-terminal solid-state semiconductor device that presents a low impedance to current flow in one direction and a high impedance to current flow in the opposite direction. These properties allow the diode to be used as a one-way current valve in electronic circuits. RECTIFIERS are a class of circuits whose purpose is to convert ac waveforms (usually sinusoidal and with zero average value) into a waveform that has a significant non-zero average value (dc component). Simply stated, rectifiers are ac-to-dc energy converter circuits. Most rectifier circuits employ diodes as the principal elements in the energy conversion process; thus the almost inseparable notions of diodes and rectifiers.

Most diodes are made from a host crystal of silicon (Si) with appropriate impurity elements introduced to modify, in a controlled manner, the electrical characteristics of the device. These diodes are the typical pn –junction (or bipolar) devices used in electronic circuits.

Another type is the Schottky diode (unipolar), produced by placing a metal layer directly onto the semiconductor. The metal semiconductor interface serves the same function as

the pn-junction in the common diode structure. Other semiconductor materials such as gallium-arsenide (GaAs) and silicon-carbide (SiC) are also in use for new and specialized applications of diodes. Detailed discussion of diode structures and the physics of their operation can be found in later paragraphs of this section. The electrical circuit symbol for a bipolar diode is shown in Fig.1.

The polarities associated with the forward voltage drop for forward current flow are also included. Current or voltage opposite to the polarities is considered to be negative values with respect to the diode conventions show the current voltage dependencies of typical diodes. The diode conducts forward current with a small forward voltage drop across the device, simulating a closed switch.

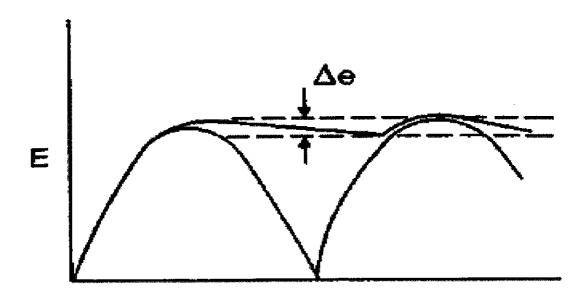

The relationship between the forward current and forward voltages approximately given by the Shockley diode equation [Shockley, 1949]: Boltzmann's constant, and T is the temperature of the semiconductor. Around the knee of the curve in Fig.2is a positive voltage that is termed the turn-on or sometimes the threshold voltage for the diode. This value is an approximate voltage above which the diode is considered turned "on" and can be modeled to first degree as a closed switch with constant forward drop. Below the threshold voltage value the diode is considered weakly conducting and approximated as an open switch.

Reverse voltage applied to the diode causes a small leakage current (negative according to the sign convention) to flow that is typically orders of magnitude lower than current in the forward direction. The diode can withstand reverse voltages up to a limit determined by its physical construction and the semiconductor material used beyond this value the reverse voltage imparts enough energy to the charge carriers to cause large increases in current. The mechanisms by which this current increase occurs are impact ionization (avalanche) [McKay, 1954] and a tunneling phenomenon (Zener breakdown) [Moll, 1964]. Avalanche breakdown results in large power dissipation in the diode, are generally destructive, and should be avoided at all times. Both breakdown regions are superimposed in Fig.3.2 for comparison of their effects on the shape of the diode characteristic curve. Avalanche